全部

▼

搜索

熱搜:

位置:中冶有色 >

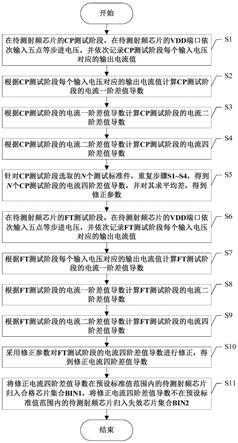

> 射頻芯片篩測(cè)方法與流程

721

編輯:中冶有色技術(shù)網(wǎng)

來(lái)源:成都嘉納海威科技有限責(zé)任公司

721

編輯:中冶有色技術(shù)網(wǎng)

來(lái)源:成都嘉納海威科技有限責(zé)任公司

分享 0

分享 0

舉報(bào) 0

舉報(bào) 0

收藏 0

收藏 0

反對(duì) 0

反對(duì) 0

點(diǎn)贊 0

點(diǎn)贊 0

中冶有色技術(shù)平臺(tái)

中冶有色技術(shù)平臺(tái) 2025年03月21日 ~ 23日

2025年03月21日 ~ 23日  2025年03月28日 ~ 30日

2025年03月28日 ~ 30日  2025年03月28日 ~ 30日

2025年03月28日 ~ 30日  2025年03月29日 ~ 31日

2025年03月29日 ~ 31日  2025年04月11日 ~ 13日

2025年04月11日 ~ 13日