光刻系統(tǒng)(圖片來(lái)源:ASML 官網(wǎng))

據(jù)報(bào)道,由imec和ASML組成的imec-ASML 聯(lián)合High NA實(shí)驗(yàn)室在開(kāi)發(fā)圖案化和蝕刻工藝�、篩選新的光刻膠和底層材料、改進(jìn)計(jì)量和光掩模技術(shù)方面取得了進(jìn)展��。

“Imec 正在與 ASML 就 High-NA 技術(shù)展開(kāi)合作��,因?yàn)?ASML 正在構(gòu)建其第一臺(tái)原型 0.55NA EUV 光刻掃描儀 EXE:5000����,”Imec 首席執(zhí)行官 Luc Van den Hove 日前表示,“與當(dāng)前的 0.33NA EUV 光刻相比��,High-NA EUV 光刻預(yù)計(jì)將打印2nm 以上的邏輯芯片所需的最關(guān)鍵功能具有更少的圖案化步驟���。我們的職責(zé)是與全球圖案化生態(tài)系統(tǒng)緊密合作�����,確保及時(shí)提供先進(jìn)的抗蝕材料��、光掩模�����、計(jì)量技術(shù)�、(變形)成像策略和圖案化技術(shù)——充分受益于 High-NA光刻機(jī)提供的分辨率增益�。”

在今年的 SPIE 先進(jìn)光刻會(huì)議上�����,這個(gè)聯(lián)合實(shí)驗(yàn)室將在 High-NA EUV 光刻領(lǐng)域有 12 個(gè)貢獻(xiàn)�����。

減少圖案粗糙度和缺陷的工藝和材料優(yōu)化

在對(duì)第一個(gè)High-NA EUV 原型系統(tǒng)的預(yù)期中���,Imec 正在提高當(dāng)前 0.33NA EUV 圖案化技術(shù)的分辨率能力�����,以預(yù)測(cè)用于印刷細(xì)線/空間和接觸孔的更薄抗蝕劑的性能����。除了圖案塌陷之外,imec 還將線邊緣粗糙度 (LER) 確定為用薄抗蝕劑膜圖案化線/空間的最關(guān)鍵參數(shù)之一�����,并提出了減輕圖案粗糙度的策略(例如����,通過(guò)調(diào)整照明和掩模條件)。

此外����,imec 及其材料供應(yīng)商展示了在High NA 條件下篩選具有良好圖案轉(zhuǎn)移能力的新型光刻膠材料(如金屬氧化物光刻膠)和底層的結(jié)果。

他們還提出了專門的圖案化和蝕刻方案��,旨在減少缺陷和隨機(jī)印刷失敗��。(論文編號(hào) 12051-7�����;12055-4����;12056-28)

定制計(jì)量以應(yīng)對(duì)薄抗蝕劑薄膜和高吞吐量的小特征尺寸

在向更小的特征尺寸(例如�����,10nm 寬的線)和更薄的抗蝕劑膜(20nm 及以下)的轉(zhuǎn)變���,產(chǎn)業(yè)迎來(lái)了兩個(gè)重要方面對(duì)計(jì)量提出了挑戰(zhàn)���。首先�,計(jì)量學(xué)家需要應(yīng)對(duì) CD-SEM 工具大幅降低的圖像對(duì)比度���;其次���,需要對(duì)小于 10nm 的特征進(jìn)行成像(考慮到疊加性能、LER 和隨機(jī)打印失?��。?���,需要具有更高分辨率的計(jì)量工具��。

Imec 高級(jí)圖案化項(xiàng)目總監(jiān) Kurt Ronse 說(shuō):“Imec 及其合作伙伴采取了幾個(gè)方向來(lái)應(yīng)對(duì)這些挑戰(zhàn)����。他們表明����,通過(guò)調(diào)整現(xiàn)有計(jì)量工具的操作條件�,可以顯著提高圖像對(duì)比度。在深度學(xué)習(xí)框架(如基于深度學(xué)習(xí)的去噪)的支持下����,專用軟件進(jìn)一步增強(qiáng)了圖像分析和缺陷分類。最后����,通過(guò)與計(jì)量供應(yīng)商的密切合作,imec 探索了用于可靠測(cè)量小特征的替代計(jì)量技術(shù)��,例如高通量掃描探針計(jì)量和低壓像差校正 SEM�。” (論文編號(hào) 12053-2���;12053-3���;12053-5;12053-22��;12053-43;12053-64)

解決高數(shù)值孔徑 EUV 掩模的特定挑戰(zhàn)

Imec 模擬了 EUV 掩模缺陷(更具體地說(shuō)���,掩模多層波紋和吸收線邊緣粗糙度)對(duì) 22nm 節(jié)距線/空間成像的影響�����。

“從這項(xiàng)研究中可以清楚地看出�,掩模缺陷對(duì)最終晶圓圖案的影響越來(lái)越大����,這表明掩模設(shè)計(jì)規(guī)則需要變得更加嚴(yán)格���,”Kurt Ronse 補(bǔ)充道��?��!斑@些發(fā)現(xiàn)使我們能夠確定High NA EUV 光刻的掩模規(guī)格。此外�����,我們與 ASML 和我們的材料供應(yīng)商一起�,探索用于承載該圖案的掩模吸收器的新型材料(第二屆全國(guó)鋰電材料標(biāo)準(zhǔn)化在線報(bào)告會(huì))和架構(gòu)�。在這種情況下�����,我們首次進(jìn)行了曝光����,以評(píng)估使用低 n 衰減相移掩模對(duì)通孔層和線/空間成像的影響。具有低 n 吸收材料的掩模作為當(dāng)前使用的 Ta 基空白的替代品被證明可以改善晶片上的掩模 3D 效果�,從而有助于增高High NA 焦深?���!?(論文編號(hào) 12051-37;12051-51�����;12051-56)�����。

為下一代EUV光刻機(jī)做好準(zhǔn)備

半導(dǎo)體行業(yè)正在全速前進(jìn)以開(kāi)發(fā)高數(shù)值孔徑(high-NA )EUV�,但開(kāi)發(fā)下一代光刻系統(tǒng)和相關(guān)基礎(chǔ)設(shè)施仍然是一項(xiàng)艱巨而昂貴的任務(wù)。

一段時(shí)間以來(lái)��,ASML 一直在開(kāi)發(fā)其高數(shù)值孔徑 (high-NA) EUV光刻機(jī)——當(dāng)今基于 0.33 數(shù)值孔徑透鏡的 EUV 光刻系統(tǒng)的后續(xù)產(chǎn)品。ASML 新的高數(shù)值孔徑 EUV 系統(tǒng)涉及一種全新的工具�����,具有 0.55 數(shù)值孔徑的鏡頭���,分辨率為 8 納米�����,而現(xiàn)有工具的分辨率為 13 納米�。分析師表示����,0.55 NA 的EUV 工具的目標(biāo)是 2023 年的 3nm����,但我們認(rèn)為該設(shè)備不太可能在 2025 年之前投入生產(chǎn)。

TWINSCAN NXE:3600D(圖片來(lái)源:ASML 官網(wǎng))

據(jù) KeyBanc 稱���,一臺(tái)High NA 光刻機(jī)的成本預(yù)計(jì)為 3.186 億美元����,而今天的 EUV 系統(tǒng)則為 1.534 億美元。但事實(shí)上���,光刻系統(tǒng)的總成本可能會(huì)更高����,因?yàn)槲覀冃枰渌略O(shè)備���、新光掩模和不同的光刻膠來(lái)實(shí)現(xiàn)高數(shù)值孔徑 EUV����。各種供應(yīng)商都在研究這些技術(shù)�,但在這一點(diǎn)上仍然存在一些差距。

光刻設(shè)備用于對(duì)芯片上的微小特征進(jìn)行圖案化����,使芯片制造商能夠在高級(jí)節(jié)點(diǎn)上開(kāi)發(fā)更小、更快的設(shè)備�,并將更多的特征封裝到單個(gè)芯片或封裝中。直到 2018 年����,芯片制造商都使用傳統(tǒng)的光學(xué)光刻掃描儀在前沿芯片上對(duì)特征進(jìn)行圖案化。但在先進(jìn)的節(jié)點(diǎn)上,光刻的圖案化過(guò)程變得過(guò)于復(fù)雜�,這就帶來(lái)了對(duì) EUV的需求,但這還遠(yuǎn)遠(yuǎn)不夠��。

ASML使用13.5nm 波長(zhǎng)的 0.33 NA EUV 光刻機(jī)正被三星和臺(tái)積電用于生產(chǎn) 7nm 和 5nm 芯片�。英特爾也為先進(jìn)的芯片生產(chǎn)加入了 ASML 的 EUV 設(shè)備。三星和 SK 海力士正在使用 EUV 進(jìn)行 DRAM 生產(chǎn)�����。

芯片制造商將長(zhǎng)期使用今天的 EUV���。但在某些時(shí)候——例如在 3nm 節(jié)點(diǎn)之外的某個(gè)節(jié)點(diǎn)�,使用現(xiàn)有的 EUV 對(duì)未來(lái)的芯片進(jìn)行圖案化將變得更為困難���。這就是High NA 設(shè)備適合的地方�。

首先�����,英特爾認(rèn)為該技術(shù)至關(guān)重要���,并宣布計(jì)劃安裝 ASML 的第一臺(tái) 0.55 High NA EUV 光刻機(jī)。

英特爾高級(jí)副總裁兼技術(shù)開(kāi)發(fā)部總經(jīng)理 Ann Kelleher 表示:“這將帶來(lái)大量的學(xué)習(xí)��,但也將使我們能夠繼續(xù)向最小的幾何結(jié)構(gòu)發(fā)展?�!?/span>

三星和臺(tái)積電也將購(gòu)買高數(shù)值孔徑工具�。但是向High NA EUV的過(guò)渡涉及各種新的和移動(dòng)的部件?��!癏ighNA 重用了 0.33 NA EUV 的大量知識(shí)�,”Cowen 的分析師 Krish Sankar 說(shuō)����。“EUV 的引入對(duì)光刻膠來(lái)說(shuō)更具挑戰(zhàn)性�。向High NA 的遷移也更具進(jìn)化性,光刻膠的性能將不斷提高����,以滿足未來(lái)節(jié)點(diǎn)的成像要求。高數(shù)值孔徑的光學(xué)元件是新的��,但它們?nèi)匀皇欠瓷涔鈱W(xué)元件����。”

●為什么是High NA?

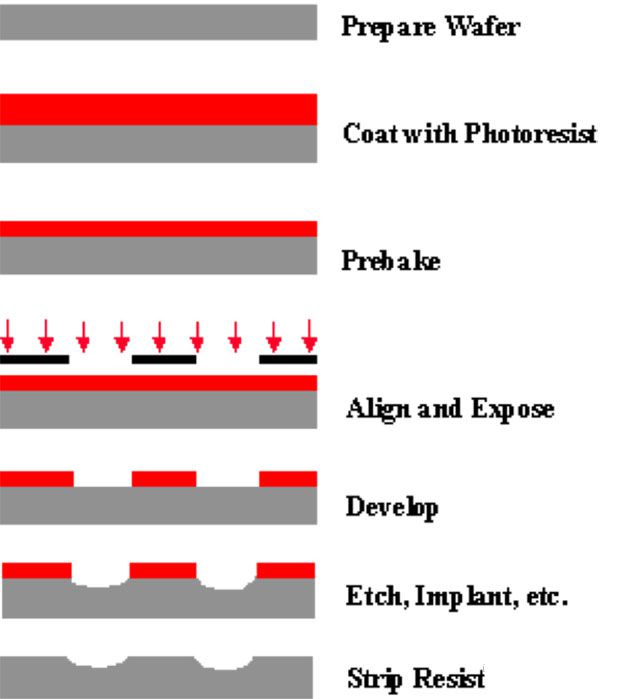

在晶圓廠中��,芯片制造商利用光刻和其他設(shè)備來(lái)生產(chǎn)芯片���。使用在設(shè)計(jì)階段生成的文件格式�����,光掩模設(shè)備創(chuàng)建一個(gè)掩模�����。掩膜是給定芯片設(shè)計(jì)的主模板��,最終被運(yùn)送到晶圓廠���。從那里,硅片被插入到涂布機(jī)/顯影劑系統(tǒng)中���。該系統(tǒng)將一種稱為光刻膠的光敏材料倒在硅片上����。

然后�,將掩模和硅片插入光刻掃描儀中。在操作中��,掃描儀產(chǎn)生光����,該光通過(guò)系統(tǒng)中的一組投影光學(xué)器件和掩模傳輸。光擊中光刻膠�,在硅片上形成圖案。

典型的光刻處理步驟序列示例��。資料來(lái)源:Chris Mack�����,F(xiàn)ractilia

多年來(lái)�����,芯片制造商使用基于193nm 波長(zhǎng)的光刻工具來(lái)圖案化高級(jí)芯片功能���。通過(guò)各種技術(shù)�,芯片制造商將 193 納米光刻技術(shù)擴(kuò)展到 7 納米��。但是在 5nm 時(shí)�,使用這些技術(shù)太復(fù)雜了���。

“打印 50nm、40nm 或 30nm 特征對(duì)于 193nm 光刻來(lái)說(shuō)是一項(xiàng)固有的艱巨任務(wù)��,” D2S首席執(zhí)行官 Aki Fujimura 說(shuō)�����?�!霸?13.5 納米波長(zhǎng)下使用 EUV 應(yīng)該會(huì)更容易��、更可行�。”

2018 年��,三星和臺(tái)積電引入了 ASML 的 0.33 NA EUV 掃描儀��,用于制造 7nm 芯片����,最近是 5nm。ASML 的 EUV 掃描儀支持 13 納米分辨率����,吞吐量為每小時(shí) 135 至 145 個(gè)晶圓 (wph)�。

但 EUV 并不完美���。該過(guò)程有時(shí)會(huì)導(dǎo)致不必要的變化和缺陷。系統(tǒng)正常運(yùn)行時(shí)間也是一個(gè)問(wèn)題���。

盡管如此���,在 7 納米,芯片制造商正在使用 EUV 來(lái)圖案化芯片特征�,間距從 40 納米開(kāi)始。供應(yīng)商正在使用基于 EUV 的單一圖案化方法�。這個(gè)想法是將芯片特征放在一個(gè)掩模上,然后使用單次光刻曝光將它們打印在晶圓上��。

芯片制造商希望盡可能擴(kuò)展 EUV 單一圖案��。EUV 單次構(gòu)圖在 32nm 到 30nm 間距達(dá)到極限����,代表 5nm 節(jié)點(diǎn)左右。

在這些間距及以上�,大致在 3nm 節(jié)點(diǎn),芯片制造商需要尋找新的選擇����,即 EUV 雙圖案����。在雙重圖案化中���,您將芯片特征分割在兩個(gè)掩模上并將它們打印在晶圓上����。這既復(fù)雜又昂貴��,但這也是晶圓廠通過(guò) 193nm 光刻技術(shù)掌握的東西��。

有些人可能希望完全避免 EUV 雙重圖案��?!艾F(xiàn)在我們正在接近 0.33 NA EUV 單次曝光的極限,為此我們正在考慮High NA EUV��,”來(lái)自TEL的工藝工程師 Arnaud Dauendorffer在最近的 SPIE 光掩模技術(shù) + EUV 會(huì)議上的演講中說(shuō)�����。

為了避免 EUV 雙重圖案化��,芯片制造商正在推動(dòng) 3nm 及以上的高數(shù)值孔徑 EUV。High-NA EUV 有望實(shí)現(xiàn)更簡(jiǎn)單的單圖案方法��。

“該工具提供了更高的分辨率���。這意味著您可以使用它打印更多功能。航拍圖像對(duì)比度可實(shí)現(xiàn)更好的局部 CD 均勻性�����,”ASML 系統(tǒng)工程總監(jiān) Jan van Schoot 在會(huì)議上的演講中說(shuō)�。

ASML 的第一個(gè)高數(shù)值孔徑 EUV 系統(tǒng) EXE:5000,具有 8nm 分辨率和 150 wph 的吞吐量�����?��?蛻舫鲐洉r(shí)間定于 2023 年��。然后����,在 2024 年底���,ASML 將出貨新版本 EXE:5200�,其吞吐量為 220 wph。

High-NA EUV 的工作原理類似于當(dāng)今的 EUV 光刻���,但存在一些關(guān)鍵差異�。與傳統(tǒng)鏡頭不同��,高數(shù)值孔徑工具包含一個(gè)變形鏡頭����,支持一個(gè)方向放大 8 倍,另一個(gè)方向放大 4 倍�。所以字段大小減少了一半。在某些情況下���,芯片制造商會(huì)在兩個(gè)掩模上加工一個(gè)芯片����。然后將掩?���?p合在一起并印刷在晶圓上,這是一個(gè)復(fù)雜的過(guò)程。

●新掩模

High-NA EUV 還需要新的光掩模類型�。EUV 和傳統(tǒng)的光學(xué)掩模是不同的。光學(xué)掩模由玻璃基板上的不透明鉻層組成�,這使得它們可以透光。

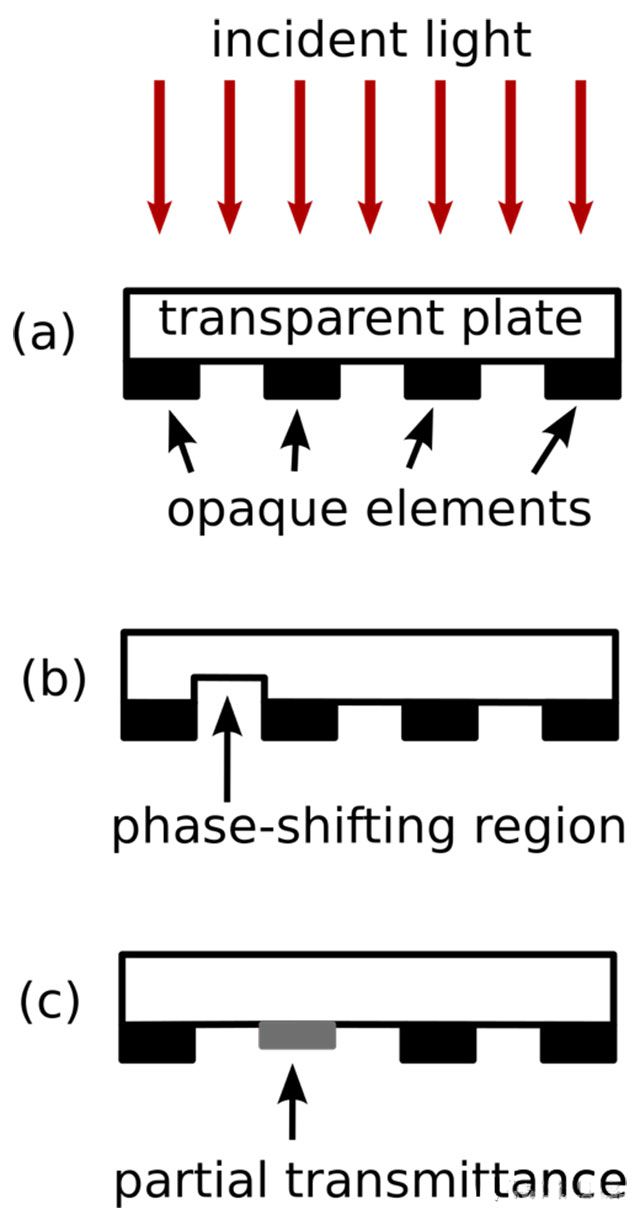

有多種類型的光學(xué)掩模���,例如二元掩模和相移掩模 (PSM)�����。

圖 2:各種類型掩碼的示意圖:(a)常規(guī)(二元)掩碼;(b) 交替相移掩模���;(c) 衰減相移掩模�。資料來(lái)源:維基百科

在二元掩模中�����,鉻在選定的位置被蝕刻���,從而暴露出玻璃基板�。鉻材料在其他地方?jīng)]有蝕刻�����。在操作中,光線照射到掩模上并穿過(guò)帶有玻璃的區(qū)域��,從而暴露出硅片�。光不會(huì)穿過(guò)鍍鉻區(qū)域。

今天也使用 PSM��?���!癙SM 有很多種,但它們的工作原理是使用相位來(lái)抵消不需要的光�,從而產(chǎn)生對(duì)比度更高的圖像,”Fractilia 的 CTO Chris Mack 說(shuō)�����。

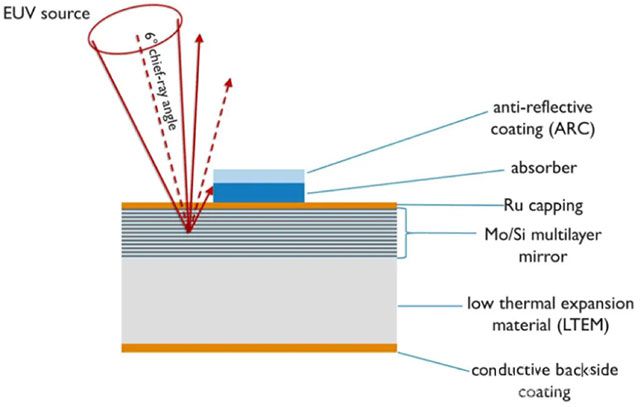

今天的 EUV 掩模是二元和反射的�����。EUV 掩模和/或坯料由 40 到 50 層硅和鉬交替薄層組成���,位于基板上��。這帶來(lái)了 250 納米到 350 納米厚的多層堆疊�����。在堆棧上�,有一個(gè)基于釕的覆蓋層,然后是一個(gè)基于鉭材料的吸收器�。

圖 3:EUV 掩模的橫截面

在掩模生產(chǎn)中,第一步是創(chuàng)建基板或掩模坯�����。由掩模坯料供應(yīng)商制造���,坯料用作掩模的基本結(jié)構(gòu)。

為了制造 EUV 掩模坯料�����,供應(yīng)商將交替的硅和鉬層沉積到基板上���。使用光化和光學(xué)檢查設(shè)備檢查掩模坯料的缺陷�。

Lasertec 銷售用于 EUV 掩模坯料的光化坯料檢測(cè) (ABI) 系統(tǒng)���。ABI 工具使用 13.5 納米波長(zhǎng)���,具有 1 納米(高度)x 40 納米(寬度)的靈敏度��,缺陷定位精度為 20 納米�����。

面向高數(shù)值孔徑 EUV����,Lasertec 正在開(kāi)發(fā)一種具有 1nm x 30nm 靈敏度的新 ABI 系統(tǒng)�����?��!拔覀兊哪繕?biāo)是 10nm 的缺陷位置��,”Lasertec USA 總裁 Masashi Sunako 在會(huì)議上的演講中說(shuō)�����。

最重要的是��,該行業(yè)正在開(kāi)發(fā)用于 3nm 及以上的新 EUV 掩模類型�����。在今天的 EUV 掩膜中����,吸收體是一種類似 3D 的特征,突出在面罩頂部�����。在操作中�,EUV 光以 6° 的角度照射掩模。反射可能會(huì)在硅片上引起陰影效應(yīng)或光掩模引起的成像像差��。此問(wèn)題稱為遮罩 3D 效果����,會(huì)導(dǎo)致不必要的圖案放置偏移���。

為了減輕這些影響��,EUV 掩模需要更薄的吸收劑�����。在現(xiàn)有的 EUV 掩模中��,鉭吸收劑的厚度為 60 納米���。它可以做得更薄�����,但限制在50nm����,這并不能解決掩膜效應(yīng)���。作為回應(yīng)����,業(yè)界正在開(kāi)發(fā)幾種新的 EUV 掩模類型�����,例如 2D�、無(wú)吸收體��、高 k����、非反射和 PSM��。

EUV PSM 似乎具有最大的動(dòng)力���。該技術(shù)解決了遮罩 3D 效果�����,同時(shí)還通過(guò)更好的對(duì)比度提高了圖像質(zhì)量�。

但是 EUV PSM 可能需要不同的材料���。

在 SPIE Photomask/EUV 會(huì)議上的演講中���,漢陽(yáng)大學(xué)的研究人員描述了一種相移 EUV 掩模,它由基板上的釕和硅交替層組成���。釕覆蓋層位于多層結(jié)構(gòu)的頂部���,然后是鉭-硼蝕刻停止層,以及作為相移材料的釕合金���。

在一篇論文中����,Hoya 開(kāi)發(fā)了各種衰減相移型吸收器并評(píng)估了其性能��?��!癙SM 期望帶來(lái)成像增益�,”來(lái)自 Hoya 的 Ikuya Fukasawa 在一次演講中說(shuō)�����?����!暗珵榱碎_(kāi)發(fā) EUV PSM 坯料�����,我們必須滿足很多要求�����。吸收材料必須具有小的粗糙度和高的抗掩模清潔的耐久性。當(dāng)然�����,吸收體必須在掩模工藝中蝕刻���?����!?/span>

與 EUV PSM 一樣��,High k 掩模也在研發(fā)中���。High k EUV 掩膜類似于今天的 EUV 掩膜。該行業(yè)正在探索鎳等其他材料���,而不是鉭吸收器���。更薄的鎳吸收劑可以減輕掩模效應(yīng),但這種材料很難使用。

與此同時(shí)���,初創(chuàng)公司 Astrileux 最近描述了一種使用釕材料的新型非反射 EUV 掩模。Astrileux 首席執(zhí)行官 Supriya Jaiswal 表示:“我們的掩膜在黑暗區(qū)域更暗�,在清晰區(qū)域更亮,并且整體背景照明和泄漏更少����。”

Astrileux 還描述了一種 2D 掩膜�,其中吸收器結(jié)合在坯料中。這家初創(chuàng)公司還談到了無(wú)流子掩膜���。所有這些都在研發(fā)中�。

就目前而言�����,芯片制造商將繼續(xù)將現(xiàn)有的 EUV 掩模/空白結(jié)構(gòu)用于現(xiàn)有的 0.33 NA EUV 工具�����。然后在某個(gè)時(shí)候芯片制造商可能會(huì)為 0.33 EUV 插入 EUV PSM�����。當(dāng)高數(shù)值孔徑 EUV 準(zhǔn)備就緒時(shí),芯片制造商可能會(huì)使用 PSM���。High k 和其他掩膜類型也是可能的�。

Hoya Group 的 Hoya LSI 總裁 Geoff Akiki 說(shuō):“隨著您的發(fā)展�,有幾種方法,無(wú)論是相移��、低 n 還是高 k����。”?“這里真正的訣竅將是集成并使其在制造中發(fā)揮作用����,將其作為產(chǎn)品推出。例如���,你有像平坦度這樣的事情��,我們花了很多時(shí)間擔(dān)心�。你有缺陷����,我們都在談?wù)?�。從某種意義上說(shuō)����,所有這些東西的選擇就像試圖調(diào)整一個(gè)制程窗口�。這是讓您最終獲得可用的東西的原因�,而不是在理想條件下?���!?/span>

●新的掩膜設(shè)備

同時(shí),掩膜坯一旦制成�,就會(huì)被運(yùn)往光掩膜供應(yīng)商。在掩模供應(yīng)商處��,對(duì)blank進(jìn)行圖案化��、蝕刻���、修復(fù)和檢查���。最后,將薄膜安裝在掩膜上。

首先���,光掩模制造商使用稱為電子束掩模寫入器的系統(tǒng)根據(jù)給定的 IC 設(shè)計(jì)在掩模上寫入圖案��。多年來(lái)�����,掩模制造商依賴基于可變形狀光束 (VSB) 技術(shù)的單光束電子束工具�����。在操作中����,將掩模插入系統(tǒng)中�,電子以射擊的形式撞擊掩模。

基于 VSB 的掩模編寫器適用于傳統(tǒng)的光學(xué)掩模�����。但是 EUV 掩模具有更小更復(fù)雜的特征���,并且 VSB 太慢而無(wú)法對(duì)其進(jìn)行圖案化����。

對(duì)于 EUV 和一些復(fù)雜的光學(xué)掩模,掩模制造商使用多光束掩模寫入器�����。IMS Nanofabrication 的多光束掩模寫入工具利用 262,000 條微小光束�,從而加快了過(guò)程。寫入時(shí)間是恒定的�����,需要 12 個(gè)小時(shí)左右來(lái)對(duì)所有掩碼進(jìn)行圖案化��。

IMS 正在推出其第二代工具��,其中包含一個(gè)新的研發(fā)版本����?��!皩?duì)于高數(shù)值孔徑 EUV 掩模制造�,新的 MBMW-301 工具將配備更多光束����,”IMS 高級(jí)顧問(wèn) Hans Loeschner 說(shuō)���。

NuFlare 還在開(kāi)發(fā)多光束掩模寫入器。這些系統(tǒng)旨在對(duì)下一代 EUV 和曲線掩模進(jìn)行圖案化����。該行業(yè)還在使用反向光刻技術(shù)(ILT)在高級(jí)光掩模上開(kāi)發(fā)曲線形狀。所謂的 ILT 掩膜對(duì)于 EUV���,尤其是高 NA 將變得很重要�。

“ILT 掩模是一種增強(qiáng)工藝窗口的方法��,以提高晶圓生產(chǎn)工藝對(duì)制造變化的彈性�����,”D2S 的 Fujimura 說(shuō)�����。

在圖案化步驟之后���,掩模結(jié)構(gòu)被蝕刻和清潔�����,形成光掩模����。在生產(chǎn)過(guò)程中,缺陷可能會(huì)出現(xiàn)在光掩模上�。

這可能有問(wèn)題。因?yàn)樵诠饪踢^(guò)程中�,來(lái)自掃描儀的光穿過(guò)光掩模,將所需的圖像投影到硅片上�����。如果掩模有缺陷����,不規(guī)則可能會(huì)印在晶圓上�。這會(huì)影響裸片的良率,甚至?xí)У粢粋€(gè)芯片�。

所以在掩模制作過(guò)程中,必須檢查光掩模是否存在缺陷��。對(duì)于傳統(tǒng)的光學(xué)掩模�����,光掩模制造商使用光學(xué)掩模檢測(cè)系統(tǒng)。Applied Materials��、KLA�����、Lasertec 和 NuFlare 銷售這些系統(tǒng)����。

光學(xué)檢測(cè)工具還可以檢測(cè) EUV 掩模。光學(xué)的問(wèn)題是分辨率��。他們可能會(huì)在 20 納米到 16 納米的半間距分辨率下失去動(dòng)力���。

作為回應(yīng)��,Lasertec 最近推出了一種使用 13.5 納米光源的光化圖案掩模檢測(cè) (APMI) 系統(tǒng)�����。較小的波長(zhǎng)使系統(tǒng)能夠定位 EUV 掩模的亞 20 納米缺陷�����。

Lasertec 還在開(kāi)發(fā)用于高數(shù)值孔徑 EUV 掩模的 APMI 系統(tǒng)��?!靶碌墓鈱W(xué)器件、探測(cè)器和系統(tǒng)設(shè)計(jì)已經(jīng)完成���,”Lasertec 的 Sunako 說(shuō)�����。該工具計(jì)劃于 2023/2024 年推出��。

除了光學(xué)和 APMI���,客戶還有另一種 EUV 掩模檢測(cè)選項(xiàng)。那就是KLA 和 NuFlare 正在開(kāi)發(fā)多光束電子束掩模檢測(cè)工具�。

NuFlare 正在開(kāi)發(fā)一種具有 100 個(gè)光束的多光束檢測(cè)系統(tǒng),計(jì)劃于 2023 年推出��?!办`敏度為 15 納米�����。檢查時(shí)間為每個(gè)掩膜檢查周期 6 小時(shí),”NuFlare 的杉森忠行說(shuō)�����。

總而言之��,對(duì)于當(dāng)前和未來(lái)的 EUV 掩模����,光掩模制造商將使用所有檢測(cè)類型——光化、電子束和光學(xué)��。

和檢查一樣����,掩膜修復(fù)也很關(guān)鍵。如果掩模有缺陷��,光掩模制造商可以使用掩模修復(fù)系統(tǒng)修復(fù)它們�����。掩模修復(fù)工具有兩種類型���,電子束和納米加工���。兩者是互補(bǔ)的�。

對(duì)于高級(jí)節(jié)點(diǎn)����,蔡司推出了一種使用電子束技術(shù)的新掩模修復(fù)工具。該系統(tǒng)可修復(fù)掩膜和 10 納米及更小尺寸擠壓件上半間距低至 60 納米的缺陷�。

同時(shí),布魯克提供使用納米加工技術(shù)的掩模修復(fù)工具��。這些系統(tǒng)包含一個(gè)微小的尖端來(lái)修復(fù)掩模缺陷��。

所有掩模修復(fù)工具都必須跟上先進(jìn)節(jié)點(diǎn)的縮小特征和缺陷尺寸����。他們還必須處理各種材料?��!斑@些工藝的材料(第二屆全國(guó)鋰電材料標(biāo)準(zhǔn)化在線報(bào)告會(huì))獨(dú)立性對(duì)于去除掉落和其他殘留的軟缺陷污染至關(guān)重要����,因?yàn)椴牧咸匦酝ǔJ俏粗?�,”布魯克技術(shù)總監(jiān)杰夫·勒克萊爾 (Jeff LeClaire) 說(shuō)�����。

●需要新光刻膠

光刻膠對(duì)于光刻也很重要�����。芯片制造商需要具有良好分辨率 [R]���、低線寬粗糙度 [L] 和靈敏度 [S] 的光刻膠����。

該行業(yè)已經(jīng)開(kāi)發(fā)出用于光刻的光刻膠����。但對(duì)于 EUV 來(lái)說(shuō),情況就不同了��。這主要?dú)w咎于同時(shí)獲得所有這三個(gè)參數(shù)是很困難的���,因?yàn)樗鼈兪窍嗷リP(guān)聯(lián)的����,而且一個(gè)參數(shù)的改進(jìn)通常至少會(huì)降低其他參數(shù)中的一個(gè)——通常被稱為 RLS 權(quán)衡關(guān)系。

正在生產(chǎn)的 EUV 光刻膠基于兩種技術(shù)——化學(xué)放大抗蝕劑 (CAR) 和金屬氧化物���。用于光學(xué)和 EUV 的 CAR 涉及一個(gè)復(fù)雜的過(guò)程��。當(dāng)光子撞擊掃描儀中的光刻膠時(shí)���,會(huì)引起連鎖反應(yīng)。

“反應(yīng)級(jí)聯(lián)的一部分涉及初始光子的化學(xué)放大�,其中光子首先轉(zhuǎn)化為幾個(gè)電子,每個(gè)入射光子最終會(huì)產(chǎn)生幾個(gè)光酸分子����。CAR的優(yōu)勢(shì)在于可以通過(guò)增加每個(gè)光子產(chǎn)生的光酸分子的數(shù)量來(lái)提高光刻膠的靈敏度。然而�����,這些額外的酸將越來(lái)越遠(yuǎn)離原始光子的位置���,導(dǎo)致圖像模糊���,從而降低分辨率并增加線邊緣粗糙度。

金屬氧化物光刻膠不太成熟����,但它們具有一些優(yōu)勢(shì)�����。例如,Inpria 的金屬氧化物光刻膠基于氧化錫結(jié)構(gòu)��,可以更有效地捕獲 EUV 光子�����。

今天����,業(yè)界正在尋找一種滿足高數(shù)值孔徑 EUV 的 RLS 要求的光刻膠。這仍然是一項(xiàng)正在進(jìn)行的工作�����。Paul Scherrer 研究所 (PSI) 和 ASML 的研究人員正在使用干擾 EUV 光刻系統(tǒng)篩選高 NA 的各種抗蝕劑����。研究人員用各種抗蝕劑圖案化線條和空間,希望獲得 8nm 半間距分辨率�。

PSI 最近展示了來(lái)自未公開(kāi)供應(yīng)商的 CAR 和非 CAR 抗蝕劑的結(jié)果��。使用大約 60mJ/cm2 的 CAR 劑量����,PSI 的 R&D EUV 系統(tǒng)在 13nm 半間距處形成清晰的線條和空間圖案�����,但在 12nm 處遇到輕微橋接�����,在 11nm 處出現(xiàn)圖案塌陷�����。PSI 的研究員 Timothée Allenet 在一次演講中說(shuō):“我們已經(jīng)將化學(xué)放大抗蝕劑的最終分辨率從 12 納米提高到 11 納米�����,只需優(yōu)化底層�����?!?/span>

同時(shí)���,根據(jù) PSI 的說(shuō)法,在 30mJ/cm2 劑量下��,分子光刻膠在 13nm 處表現(xiàn)出良好的圖像��,但由于在 12nm 處圖案坍塌��,它們遇到了故障��。

然后�����,使用不同的劑量���,金屬氧化物光刻膠在低至 12nm 處表現(xiàn)出良好的效果?��!霸?11nm 半節(jié)距處�����,我們有輕微的橋接��,然后在 10nm 處出現(xiàn)分辨率瓶頸��,”Allenet 說(shuō)�����。

從好的方面來(lái)說(shuō)��,今天 0.33 NA EUV 的阻力并沒(méi)有停滯不前�����,并且正在改善�。例如,TEL 描述了 CAR 和金屬氧化物抗蝕劑的新工藝��。

“總而言之�����,涂布機(jī)/顯影劑工藝與優(yōu)化的底層薄膜一起顯示出 CAR 圖案坍塌裕度的改善����。優(yōu)化的底層改善了金屬氧化物抗蝕劑的缺陷密度、產(chǎn)量和粗糙度,”TEL 的 Kanzo Kato 說(shuō)��。

●結(jié)論

其他 EUV 技術(shù)也在開(kāi)發(fā)中���,例如薄膜��。薄膜用于覆蓋掩膜���,防止顆粒落在面罩上。

ASML 開(kāi)發(fā)了新的 EUV 薄膜�����。與此同時(shí)�,Imec 的碳納米管薄膜在 ASML 的 EUV 掃描儀上顯示出 97.7% 的透射率�����。單壁和多壁薄膜都是有前途的���。

“兩種類型的表現(xiàn)都很好����,在 CD 均勻性����、LWR 和耀斑方面���,與無(wú)防護(hù)膜參考相比,成像差異很小�。根據(jù)測(cè)得的這些薄膜的 EUV 吸收范圍從 95.3% 到 97.7%,預(yù)計(jì)劑量會(huì)略有增加�����,”Imec 技術(shù)人員的主要成員 Emily Gallagher 說(shuō)�����。

毫無(wú)疑問(wèn)��,很多人正在為高數(shù)值孔徑 EUV 開(kāi)發(fā)其他技術(shù)����。不管所有部分是否到位,芯片制造商都表示���,2023 年及以后的芯片生產(chǎn)需要高數(shù)值孔徑 EUV��。

盡管如此����,研發(fā)成本才剛剛開(kāi)始堆積。沒(méi)有多少人買得起這些系統(tǒng)����。此外,還有待觀察的是����,High NA 光刻機(jī)何時(shí)真正投入生產(chǎn)。

2354

2354

0

0

分享 0

分享 0

舉報(bào) 0

舉報(bào) 0

收藏 0

收藏 0

反對(duì) 0

反對(duì) 0

點(diǎn)贊 0

點(diǎn)贊 0

中冶有色技術(shù)平臺(tái)

中冶有色技術(shù)平臺(tái)